Projektgruppen und Arbeiten

Zu vergebende Arbeiten

Bachelor/

Master thesis: Implement a systemC based router for

Multicore Network-on-chip

Master Thesis/ Masterarbeit:

Simulation Environment for Time-Triggered Ethernet

|

|

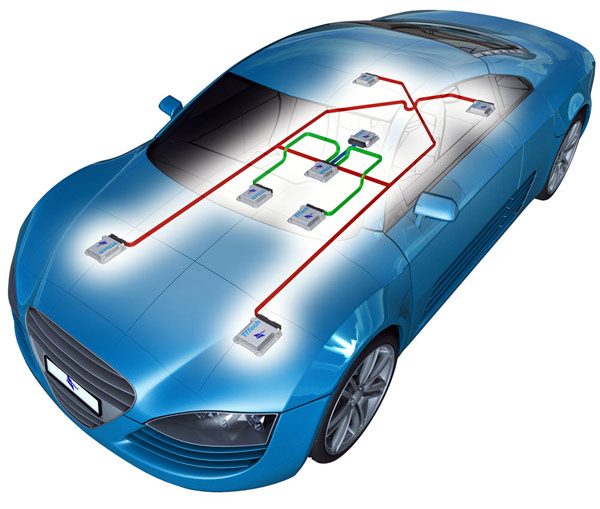

The continuous growth of electronics in the automotive industry lead to a high number of different bus systems. These are largely incompatible with each other and are each optimized to the requirements of a particular communication scenario. However, since system-wide coordination is required between these systems a central gateway is available in almost all vehicles to support the exchange of messages. For reasons of simplicity and also for cost reduction, it is desirable to reduce the number of networking technologies. Since Ethernet is widely used in many areas, it is a cost-effective standard and has long been proven, it is a natural candidate for in-vehicle networks (e.g., replacing FlexRay, MOST, high-speed CAN, ByteFlight). In the automotive environment, the reliable functioning of safety-relevant systems is considered essential. Therefore, a technology is needed also in terms of communication, which can support a quality of service guarantee. Since Ethernet does not support applications with real-time and safety requirements, Ethernet extensions with predictable timing were developed. Time-Triggered Ethernet (TTEthernet) is a real-time Ethernet extension that was standardized by the Society of Automotive Engineers (SAE). It supports message exchanges with bounded transmission delays, low jitter and high channel utilization. |

Two Mastertheses in the

european project UniversAAL

|

|

Topic

#1: Implement an error detector using

message classification

Topic #2: Implement

the Situation Reasoner to handle

detected errors

|

Gemeinsame Diplomarbeit

mit Daimler

|

|

Die Erweiterung einer Autosar OS 3.x Umsetzung um Multicorefähigkeiten soll durchgeführt werden. Das OS ist als Wrapper-Schicht auf Basis der Linux Posix API umgesetzt, unterstützt aber nur eine CPU Core. Für die Benchmarks muss man sich in die Autosar OS Spezifikation einarbeiten. Für die Umsetzung der Multicore OS Erweiterung benötigt man zusätzlich detaillierte Posix Realtime Kenntnisse, die ggf. erarbeitet werden müssen. Als Basis dient die KPIT/Cummins Autosar OS Implementierung. |

Dynamische Konfiguration

eines zeitgesteuerten Network-on-a-Chip

|

|

Das Zeitgesteuerte Network-on-a-Chip (NoC) bietet die Grundlage zur Integration von IP-Cores mit zeitlicher Vorhersehbarkeit und inhärenter Fehlerisolation. Dadurch eignet es sich ideal für sicherheitsrelevante eingebettete Echtzeitsysteme. Der Nachrichtenaustausch wird durch einen Kommunikationsplan definiert, welcher die globalen Zeitpunkte für die Übertragung von Nachrichten festlegt. Das Ziel dieser Abschlussarbeit ist die Erweiterung des Zeitgesteuerten NoCs zur dynamischen Veränderung des Kommunikationsplans. Somit wird die Anpassung an neue Umgebungsbedingungen oder die Veränderungen der Ressourcenverfügbarkeit möglich. Als Grundlage dient die vorhandene Implementierung des NoCs in einem FPGA. Ansprechpartner: Prof. Dr. Roman Obermaisser |

Experimentelle

Evaluirierung eines CAN-Netzwerkes auf Basis eines

Sternkopplers

|

|

Controller Area Network (CAN) ist das am weitesten verbreitete Protokoll in der Automobilelektronik. Zur Überwindung von Limitationen in CAN betreffend Fehlerisolation, Skalierbarkeit und Diagnose wurde ein CAN-Router auf Basis eines FPGAs entwickelt, welcher Kompatibilität zu existierenden Steuergeräten sicherstellt. Bei Verwendung des Sternkopplers wird die Bustopologie konventioneller CAN-Netzwerke durch eine Sterntopologie ersetzt. Die Ziele des Sternkopplers sind die Erhöhung der Skalierbarkeit durch bessere Bandbreitennutzung und Fehlerisolation durch das Blockieren fehlerhafter Nachrichten (z.B. bei Verletzung des spezifizierten minimalen Ankunftsabstands). Im Rahmen einer Abschlussarbeit sollen diese Eigenschaften des CAN-Routers (z.B. Bandbreite, Latenz, Fehlerisolation) experimentell evaluiert werden. Zu diesem Zweck ist das Design des CAN-Routers auf Basis eines FPGAs zu instanziieren und zu konfigurieren, sowie ein verteiltes System aufzubauen. Die Endgeräte sollen ein definiertes Kommunikationsverhalten am CAN-Netzwerk erzeugen und resultierende Eigenschaften aufzeichnen (z.B. Nachrichtenlatenz, Nachrichtenverluste). Ansprechpartner: Prof. Dr. Roman Obermaisser |

Integration von garantierter Kommunikation und Best-effort Kommunikation in einem zeitgesteuerten Network-on-a-Chip

|

Das zeitgesteuerte Network-on-a-Chip (NoC) bietet die Grundlage zur Integration von IP-Cores mit zeitlicher Vorhersagbarkeit und inhärenter Fehlerisolation. Dadurch eignet sich dieses NoC ideal für sicherheitsrelevante eingebettete Echtzeitsysteme. Der Nachrichtenaustausch wird durch einen Kommunikationsplan definiert, welcher die globalen Zeitpunkte für die Übertragung von Nachrichten festlegt. Das Ziel dieser Abschlussarbeit ist die Erweiterung des zeitgesteuerten NoCs um Best-effort Kommunikationskanäle. Diese Kommunikationskanäle sollen jene Bandbreite verwenden, welche von der garantierten zeitgesteuerten Kommunikation unbenutzt bleibt. Hierdurch entsteht eine optimale Unterstützung für Mixed-Criticality Applikationen, welche sicherheitsrelevante und nicht-sicherheitsrelevante Dienste enthalten. Als Grundlage dient die vorhandene Implementierung des NoCs in einem FPGA. Ansprechpartner: Prof. Dr. Roman Obermaisser |

FPGA Integrated Embedded Systems using the LEON Processor

|

The goal of this Master Thesis is the study on FPGA implemented architectures with focus on power consumption, and the mastering of the LEON processor under Xilinx Virtex technology for the execution environment of an integrated embedded system. In the initial phase, the student will study the theoretical static and dynamic power consumption on an FPGA, as well as the ways to simulate and measure these consumptions. Then, we will integrate the VHDL implemented LEON3 or LEON4 processor core of the European Space Agency (ESA) into a Xilinx Virtex device. In a third phase, the work will require the integration of the processor on the Time-Triggered System-on-Chip (TTSoC) architecture, generating a LEON based multi-core system. At the same time, an embedded hypervisor (e.g., Xtratum) will be included into an alternative single LEON processor architecture providing a system with several virtual partitions. At the final stage, the student will measure the different power consumption of both approaches using an embedded application. The project occurs in cooperation with IKERLAN www.ikerlan.es. Part of the work on the master thesis can be performed at IKERLAN Research Center in Spain. In this case, there is the opportunity for financial support. English language is required. Ansprechpartner: Prof. Dr. Roman Obermaisser |

Erstellung einer Datenbank von Nutzerdaten und deren Auswertung

|

Erstellung einer Software zur Erfassung von Nutzerdaten Erfassung von Nutzerdaten und Erstellung einer Datenbank Auswertung der aufgenommenen Nutzerdaten (Erstellung einer Schnittstelle) Diese Abschlussarbeit wird gemeinsam mit Bosch Sensortec GmbH mit Sitz in Reutlingen angeboten. Es besteht im Rahmen der Abschlussarbeit die Möglichkeit für eine finanzielle Unterstützung durch Bosch. Einarbeitung in ein Betriebssystem eines aktuellen Mobiltelefons Ansprechpartner: Prof. Dr. Roman Obermaisser |

laufende Arbeiten

Projektgruppe

|

Im Rahmen einer Projektgruppe besteht in der Fachgruppe für Eingebettete Systeme die Möglichkeit die Entwicklung verteilter eingebetteter Systeme in der Automobilindustrie zu verstehen und anhand konkreter Beispielapplikationen praktisch umzusetzen.Die Arbeit der Projektgruppe wird anhand moderner Hardware- und Softwareplattformen erfolgen, welche auch in der Automobilindustrie zum Einsatz kommen. Weitere Informationen |

Abgeschlossene

Arbeiten

High

Assureable Computing

Platform based on a Time

Triggered Network an a Chip

Das zeitgesteuerte Network-on-a-Chip (NoC) bietet die Grundlage zur Integration von IP-Cores mit zeitlicher Vorhersagbarkeit und inhärenter Fehlerisolation. Ziel dieser Arbeit ist die Weiterentwicklung dieses NoC zu einer „High Assureable Computing Platform“, welche für Assurance nach dem DO-254 Standard geeignet ist und gleichzeitig den Einsatz von verschiedenen (non-assured) COTS IP-Cores unterstützt. Diese Abschlussarbeit wird gemeinsam mit EADS angeboten. Es besteht im Rahmen der Abschlussarbeit die Möglichkeit einer Anstellung für 6 Monate bei EADS (700 Euro pro Monat). |